一、什么是信號完整性?為什么高速PCB必須重點關注?

在傳統低速電路中,PCB只要“電氣連接正確”,系統通常就能正常工作。

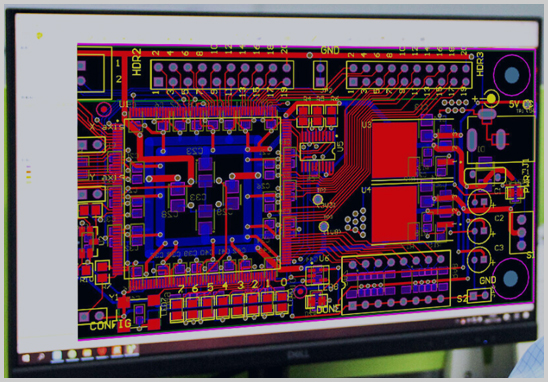

當信號的上升沿足夠快時,PCB走線不再是理想導線,而是具有分布參數的傳輸線。此時,任何不合理的設計,都會直接影響信號波形,這就是信號完整性(Signal Integrity, SI)問題。

工程經驗與行業文獻普遍認為:

當信號上升沿時間 ≤ 走線傳播延遲的 1/6~1/10 時,必須按高速信號進行設計

這也是為什么 DDR、PCIe、USB、LVDS、SerDes 等接口,對PCB設計要求極高。

二、高速PCB設計中,常見的信號完整性問題有哪些?

從實際項目經驗來看,高速PCB中最容易出現的問題主要集中在以下幾類:

1. 信號反射

由于阻抗不連續,信號在走線中來回反射,造成過沖、欠沖和振鈴。

常見誘因包括:

- 阻抗未受控

- 過孔數量過多

- BGA 扇出不合理

- 連接器或接口突變

2. 串擾(Crosstalk)

相鄰信號線之間發生電磁耦合,導致誤觸發或時序錯誤。

多發生在:

- 高速并行總線

- 差分線間距不足

- 信號線參考層不連續

3. 時序偏移(Skew)

多條相關信號到達時間不一致,影響數據采樣窗口。

典型場景:

- DDR 地址 / 數據線

- 差分信號對內不等長

4. 電源完整性不足引起的信號問題

電源噪聲通過芯片耦合到信號通道,造成抖動、誤碼。

三、解決高速PCB信號完整性問題的核心設計思路

高速PCB設計不是“補救式優化”,而是系統性規劃。

核心可以歸納為五個關鍵詞:層疊、阻抗、走線、過孔、電源。

四、高速PCB信號完整性優化的關鍵方法

1. 層疊結構設計:決定信號質量的基礎

在高速PCB設計中,層疊結構優先于走線規則。

合理層疊的基本原則是:

- 高速信號層必須緊鄰完整參考地層

- 電源層與地層成對布置,降低電源回路阻抗

- 避免高速信號跨分割地或跨電源島

典型高速多層板(如 8 層板)結構示例:

- 頂層:高速信號

- 內層:完整地

- 中間層:高速/中速信號

- 內層:電源

- 底層:低速信號

這種結構可以顯著改善回流路徑連續性。

2. 阻抗控制:避免反射的核心手段

高速信號設計的本質之一,就是阻抗匹配。

常見阻抗要求包括:

- 單端信號:50Ω

- 差分信號:90Ω / 100Ω

影響阻抗的因素主要有:

- 線寬、線距

- 介質厚度

- 介質常數(Dk)

- 銅厚

- 層疊結構

因此在PCB設計階段,需要:

- 根據板材與層疊進行阻抗計算

- 與PCB廠家確認可實現的工藝能力

- 在設計文件中明確標注阻抗要求

3. 高速信號走線規則:少就是穩

在高速PCB設計中,走線不是越“工整”越好,而是越“簡單”越好:

- 盡量短,減少延遲和損耗

- 盡量直,避免無意義繞行

- 減少過孔數量

- 避免 90° 轉角,使用 45° 或圓弧

- 差分線等長、等距、同層、同參考

對于 DDR、SerDes 等接口,還需要進行精確等長匹配。

4. BGA 與盲孔 / 埋孔設計:高速板的關鍵能力點

在高密度高速PCB中,BGA 封裝幾乎不可避免,而過孔結構直接影響信號完整性。

優化思路包括:

- 合理選擇 BGA 扇出方式

- 高速信號盡量避免使用貫穿通孔

- 使用盲孔、埋孔縮短過孔長度

- 減少過孔殘 stub 引起的反射

這也是高精密、多層高速PCB設計能力的重要體現。

5. 電源完整性設計:高速信號穩定的“隱形基礎”

大量工程案例表明,

高速信號異常,最終往往源于電源不穩定。

實用設計建議包括:

- 去耦電容靠近芯片電源引腳

- 多容值電容組合使用

- 電源與地層保持完整、低阻抗

- 避免高速信號跨越電源分割區

五、高速PCB設計,更需要“從原理圖到量產”的整體能力

高速PCB信號完整性,并不是單一技術點能解決的問題,而是貫穿:

- 原理圖理解與接口識別

- 高速信號分類與規則制定

- 層疊與阻抗方案設計

- BGA、高密度扇出設計

- BOM 建立與物料選型

- PCB 制造與 PCBA 工藝協同

這也是越來越多企業選擇專業PCB設計公司的核心原因。

六、結語:高速PCB設計,前期決定成敗

高速PCB一旦進入打樣和量產階段,修改成本會急劇上升。

把信號完整性問題前移到設計階段解決,是最省成本、也最可靠的方式。

對于只提供原理圖、希望一次把板子設計對、做穩的客戶來說,選擇具備多層、高精密、BGA及盲埋孔設計經驗的PCB設計公司,將大幅降低項目風險。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料